日本生產工程權威獎項得主力作,圖解與表格詳實,帶領工程師掌握半導體乾蝕刻技術的全貌,提升現場即戰力。

◎作者於1989年,以「有磁場微波電漿蝕刻技術的開發與實用化」受獎大河內紀念賞。1994年,以「低溫乾蝕刻設備的開發」受獎機械振興協會賞通產大臣賞。

◎圖解乾蝕刻技術的原理與實務,讓你一讀即懂。

◎由製程直到設備、新技術,更進一步設置有關電漿損傷的章節,以便理解全貌並了解乾蝕刻今後的課題與展望。

針對半導體乾蝕刻技術涉及的電漿物理、化學、材料、電磁等複雜現象,循序解析,詳解各環節的連帶影響,提升現場即時應變的作戰能力,為優秀工程師養成必備的工具書!

非等向性蝕刻是如何實現?為何Si的蝕刻使用Cl2及HBr,而SiO2的蝕刻則使用氟碳系列的氣體?為何Poly-Si及Al的蝕刻使用ICP(電感耦合式電漿)之類的高密度電漿,而SiO2的蝕刻則使用中密度電漿於間距狹窄的平行板型蝕刻機?

本書告訴你這些連現場資深乾蝕刻工程師都不見得充分理解的知識。

從乾蝕刻技術的基礎講到應用,讓初學者容易理解與整理;對於已有程度、經驗的工程師而言,讀之更加能理解、掌握乾蝕刻技術的全貌。

《半導體乾蝕刻技術》精彩內容請看:www.pressstore.com.tw/freereading/9789863581291.pdf

作者介紹

作者簡介

野尻一男(Nojiri Kazuo)

■1973年 群馬大學工學部電子工學科畢業。

■1975年 群馬大學大學院工學研究科碩士課程修畢。

■1975年 進入日立製作所。在半導體事業部從事CVD、元件整合、乾蝕刻的研究開發。尤其是關於ECR電漿蝕刻、充電損傷,進行先驅的研究。而且擔任技術開發的領導,歷任許多經理職務。

■2000年 進入Lam Research公司擔任董事‧CTO至今。

主要受獎

■1989年 以「有磁場微波電漿蝕刻技術的開發與實用化」受獎大河內紀念賞。

■1994年 以「低溫乾蝕刻設備的開發」受獎機械振興協會賞通產大臣賞。

主要著作

《先端電氣化學》(丸善)共著

《半導體プロセスにおけるチャージング・ダメージ》(リアライズ社)共著

譯者簡介

倪志榮(Ni, Chih-Jung)

■1988年 國立清華大學畢業

■1991年 中日交流協會留日獎學生

■1993年 日本東京大學工學院碩士

■2014年 中部科學園區模範勞工

■曾任地球村美日語中心日語講師

現職華邦電子公司模組技術發展部經理,從事DRAM與Flash的製程研發。

野尻一男(Nojiri Kazuo)

■1973年 群馬大學工學部電子工學科畢業。

■1975年 群馬大學大學院工學研究科碩士課程修畢。

■1975年 進入日立製作所。在半導體事業部從事CVD、元件整合、乾蝕刻的研究開發。尤其是關於ECR電漿蝕刻、充電損傷,進行先驅的研究。而且擔任技術開發的領導,歷任許多經理職務。

■2000年 進入Lam Research公司擔任董事‧CTO至今。

主要受獎

■1989年 以「有磁場微波電漿蝕刻技術的開發與實用化」受獎大河內紀念賞。

■1994年 以「低溫乾蝕刻設備的開發」受獎機械振興協會賞通產大臣賞。

主要著作

《先端電氣化學》(丸善)共著

《半導體プロセスにおけるチャージング・ダメージ》(リアライズ社)共著

譯者簡介

倪志榮(Ni, Chih-Jung)

■1988年 國立清華大學畢業

■1991年 中日交流協會留日獎學生

■1993年 日本東京大學工學院碩士

■2014年 中部科學園區模範勞工

■曾任地球村美日語中心日語講師

現職華邦電子公司模組技術發展部經理,從事DRAM與Flash的製程研發。

目錄

序言

譯者序

第1章 半導體積體電路的發展與乾蝕刻技術

1.1 乾蝕刻的概要

1.2 關於乾蝕刻的評鑑參數

1.3 在大型積體電路上乾蝕刻技術所扮演的角色

參考文獻

第2章 乾蝕刻的機制

2.1 電漿的基礎

1 電漿是什麼

2 電漿的各物理量

3 電漿中的碰撞反應過程

2.2 離子鞘以及離子鞘內的離子行為

1 離子鞘與Vdc

2 離子鞘內的離子散射

2.3 蝕刻製程的建構方法

1 乾蝕刻的反應過程

2 非等向性蝕刻的機制

3 側壁保護過程

4 蝕刻率

5 選擇比

6 總結

參考文獻

第3章 各種材料的蝕刻

3.1 閘極蝕刻

1 Poly-Si閘極蝕刻

2 晶圓面內CD均勻度的控制

3 WSi2/Poly-Si閘極蝕刻

4 W/WN/Poly-Si閘極蝕刻

5 Si基板的蝕刻

3.2 SiO2蝕刻

1 SiO2蝕刻的機制

2 SiO2蝕刻的關鍵參數

3 孔洞系列的蝕刻

4 SAC蝕刻

5 Spacer蝕刻

3.3 連線蝕刻

1 Al連線蝕刻

2 Al連線的防腐蝕處理技術

3 其它連線材料的蝕刻

3.4 總結

參考文獻

第4章 乾蝕刻設備

4.1 乾蝕刻設備的歷史

4.2 圓筒型電漿蝕刻機

4.3 CCP電漿蝕刻機

4.4 磁電管RIE

4.5 ECR電漿蝕刻機

4.6 ICP電漿蝕刻機

4.7 乾蝕刻設備的實例

4.8 靜電吸盤

1 靜電吸盤的種類以及吸附原理

2 晶圓溫度控制的原理

參考文獻

第5章 乾蝕刻損傷

5.1 導入Si表層的損傷

5.2 充電損傷

1 充電損傷的評鑑方法

2 充電的發生機制

3 各種蝕刻設備的充電評鑑與減低方法

4 起因於圖形的閘極氧化層破壞

參考文獻

第6章 新蝕刻技術

6.1 Cu 鑲嵌蝕刻

6.2 Low-k蝕刻

6.3 使用多孔型Low-k的鑲嵌連線

6.4 金屬閘極/High-k蝕刻

6.5 FinFET蝕刻

6.6 雙重圖形定義

6.7 用於3D IC的蝕刻技術

參考文獻

第7章 乾蝕刻技術今後的課題與展望

7.1 關於乾蝕刻的技術革新

7.2 今後的課題與展望

7.3 作為工程師的心理準備

參考文獻

譯者序

第1章 半導體積體電路的發展與乾蝕刻技術

1.1 乾蝕刻的概要

1.2 關於乾蝕刻的評鑑參數

1.3 在大型積體電路上乾蝕刻技術所扮演的角色

參考文獻

第2章 乾蝕刻的機制

2.1 電漿的基礎

1 電漿是什麼

2 電漿的各物理量

3 電漿中的碰撞反應過程

2.2 離子鞘以及離子鞘內的離子行為

1 離子鞘與Vdc

2 離子鞘內的離子散射

2.3 蝕刻製程的建構方法

1 乾蝕刻的反應過程

2 非等向性蝕刻的機制

3 側壁保護過程

4 蝕刻率

5 選擇比

6 總結

參考文獻

第3章 各種材料的蝕刻

3.1 閘極蝕刻

1 Poly-Si閘極蝕刻

2 晶圓面內CD均勻度的控制

3 WSi2/Poly-Si閘極蝕刻

4 W/WN/Poly-Si閘極蝕刻

5 Si基板的蝕刻

3.2 SiO2蝕刻

1 SiO2蝕刻的機制

2 SiO2蝕刻的關鍵參數

3 孔洞系列的蝕刻

4 SAC蝕刻

5 Spacer蝕刻

3.3 連線蝕刻

1 Al連線蝕刻

2 Al連線的防腐蝕處理技術

3 其它連線材料的蝕刻

3.4 總結

參考文獻

第4章 乾蝕刻設備

4.1 乾蝕刻設備的歷史

4.2 圓筒型電漿蝕刻機

4.3 CCP電漿蝕刻機

4.4 磁電管RIE

4.5 ECR電漿蝕刻機

4.6 ICP電漿蝕刻機

4.7 乾蝕刻設備的實例

4.8 靜電吸盤

1 靜電吸盤的種類以及吸附原理

2 晶圓溫度控制的原理

參考文獻

第5章 乾蝕刻損傷

5.1 導入Si表層的損傷

5.2 充電損傷

1 充電損傷的評鑑方法

2 充電的發生機制

3 各種蝕刻設備的充電評鑑與減低方法

4 起因於圖形的閘極氧化層破壞

參考文獻

第6章 新蝕刻技術

6.1 Cu 鑲嵌蝕刻

6.2 Low-k蝕刻

6.3 使用多孔型Low-k的鑲嵌連線

6.4 金屬閘極/High-k蝕刻

6.5 FinFET蝕刻

6.6 雙重圖形定義

6.7 用於3D IC的蝕刻技術

參考文獻

第7章 乾蝕刻技術今後的課題與展望

7.1 關於乾蝕刻的技術革新

7.2 今後的課題與展望

7.3 作為工程師的心理準備

參考文獻

序

自序

乾蝕刻技術作為半導體元件的微縮、高積體化的手段,與微影技術構成雙璧的關鍵技術,所參與的工程師人數也幾乎與微影相同的多。微影技術由於解析度取決於光波長和NA(透鏡的數值孔徑),比較容易理解。相對而言,乾蝕刻技術在反應室引起的現象複雜而不容易理解。此外,由於蝕刻是利用電漿的物理、化學反應進行,需要電力、物理、化學的綜合知識。演變的結果,實際上從事乾蝕刻的工程師在許多場合,仰賴著經驗和直覺做事。非等向性蝕刻是如何實現?為何Si的蝕刻使用Cl2及HBr,而SiO2的蝕刻則使用氟碳系列的氣體?為何Poly-Si及Al的蝕刻使用ICP(電感耦合式電漿)之類的高密度電漿,而SiO2的蝕刻則使用中密度電漿於間距狹窄的平行板型蝕刻機?關於這樣的事,很多初學者在不具備充分的理解及知識的情況下,突然就被送進了現場。而且,即使是乾蝕刻的資深工程師,也有並不充分理解這些事的例子。

乾蝕刻雖然往往處於隱藏在微影背後的地位,但卻是如同開頭所述與微影技術構成雙璧的關鍵技術。換言之,(l)Si、SiO2、金屬等,每種材料有特定的設備與製程技術;(2)Cu鑲嵌連線加工、新材料加工等,新的領域連續不斷的誕生;(3)使用帶電粒子的緣故所產生的電漿損傷,是降低元件良率的元凶,機制的闡明與對策是必要的;(4)當今熱門話題的雙重圖形定義,乾蝕刻比微影更為重要,左右尺寸大小的精度與偏差。因應如此各式各樣的材料,並且愈來愈高度化的加工技術,讓今後想要從事的工程師,應當對乾蝕刻技術具有充分的理解加以面對,並且需求針對初學者的教科書。

本書採用與以往書籍相異的獨特方法,將乾蝕刻技術由基礎到應用,讓初學者能夠理解的加以歸納整理。以往的乾蝕刻書籍,大多動輒偏重於艱深的電漿理論,或是反而從頭到尾羅列乾蝕刻技術的數據。本書的執筆則是盡量不使用數學式,讓初學者也能容易的理解乾蝕刻的機制。此外,由製程直到設備、新技術,考量能系統的理解。更進一步,設置電漿損傷的章節,以便能夠理解全貌,也是特徵之一。

本書不僅讓初學者能容易的理解乾蝕刻技術的原理,也能獲得更切實際的知識。此外,雖然以初學者為對象撰寫,但是對於已經累積某種程度經驗的工程師,在能夠理解乾蝕刻技術的全貌上,期望也能有所助益。本書若能對從事乾蝕刻相關工作的工程師,在工作的執行上給予方針,至感甚幸。

譯者序

譯者就職華邦電子前,曾任職於峰安金屬、林陽實業以及遠東紡織化纖總廠。當有機會聊到自己過去的職涯時,偶而會調侃自己待過金屬、玻璃、紡織、電子等四大產業,剩下養豬業還沒去過(莞爾)。根據個人親身經歷,在電子產業中,光是晶圓廠的半導體前段製程就遠比上述其他三種產業複雜,而且技術的躍進更是日新月異。如果不求進步或轉型,恐怕只有等著關廠、解散一途。

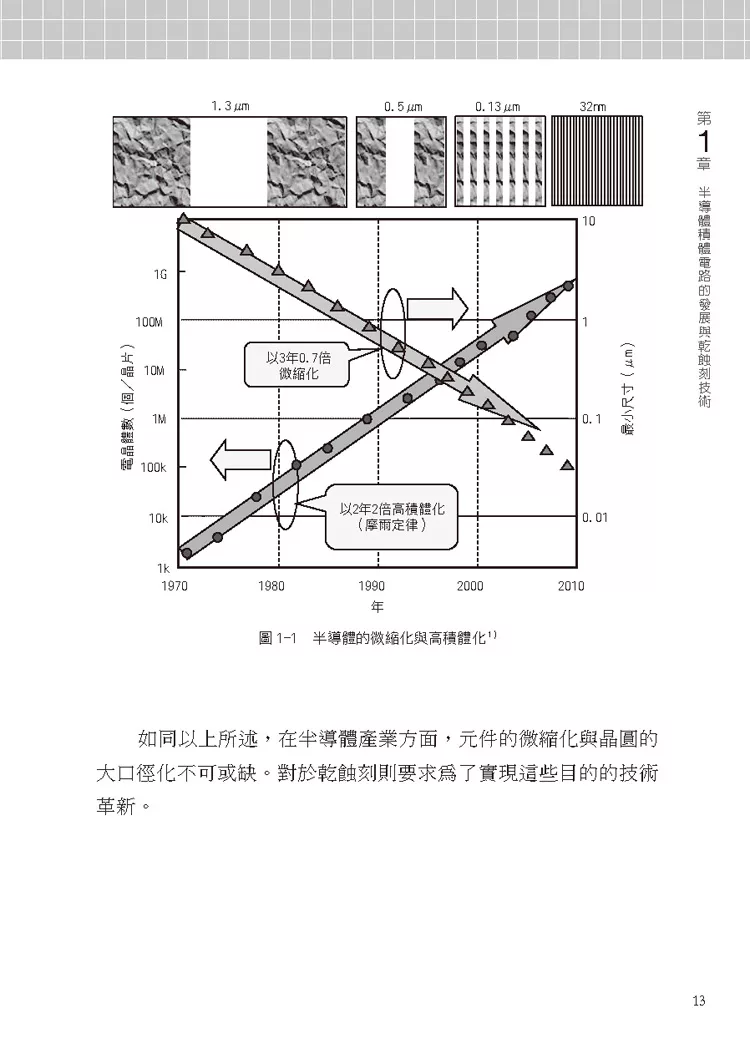

回顧1996年譯者初進半導體業,當時DRAM的量產是以0.45微米技術生產16MB記憶容量的晶片,而如今泛用型DRAM已經使用25奈米的技術量產2GB以上記憶容量的晶片,18年來推進了12個世代。

除了DRAM之外,其它諸如NOR與NAND等大宗的記憶體,以及台灣傲視全球的晶圓代工產業的主力──邏輯IC,也是不遑多讓的朝向微縮、積體化邁進。如同本書所述,其中尤以微影和乾蝕刻為關鍵技術,而乾蝕刻由於牽涉到電漿物理、化學、材料、電磁等複雜的現象,優秀工程師的養成更屬不易。

本書作者具有豐富的業界經驗,深知工程師在專業知識上的需求為何。原書的英文譯本《Dry Etching Technology for Semiconductors》也於2014年10月出版。希望本中文譯本能在半導體乾蝕刻工程師的基礎教育上,略盡棉薄之力。

乾蝕刻技術作為半導體元件的微縮、高積體化的手段,與微影技術構成雙璧的關鍵技術,所參與的工程師人數也幾乎與微影相同的多。微影技術由於解析度取決於光波長和NA(透鏡的數值孔徑),比較容易理解。相對而言,乾蝕刻技術在反應室引起的現象複雜而不容易理解。此外,由於蝕刻是利用電漿的物理、化學反應進行,需要電力、物理、化學的綜合知識。演變的結果,實際上從事乾蝕刻的工程師在許多場合,仰賴著經驗和直覺做事。非等向性蝕刻是如何實現?為何Si的蝕刻使用Cl2及HBr,而SiO2的蝕刻則使用氟碳系列的氣體?為何Poly-Si及Al的蝕刻使用ICP(電感耦合式電漿)之類的高密度電漿,而SiO2的蝕刻則使用中密度電漿於間距狹窄的平行板型蝕刻機?關於這樣的事,很多初學者在不具備充分的理解及知識的情況下,突然就被送進了現場。而且,即使是乾蝕刻的資深工程師,也有並不充分理解這些事的例子。

乾蝕刻雖然往往處於隱藏在微影背後的地位,但卻是如同開頭所述與微影技術構成雙璧的關鍵技術。換言之,(l)Si、SiO2、金屬等,每種材料有特定的設備與製程技術;(2)Cu鑲嵌連線加工、新材料加工等,新的領域連續不斷的誕生;(3)使用帶電粒子的緣故所產生的電漿損傷,是降低元件良率的元凶,機制的闡明與對策是必要的;(4)當今熱門話題的雙重圖形定義,乾蝕刻比微影更為重要,左右尺寸大小的精度與偏差。因應如此各式各樣的材料,並且愈來愈高度化的加工技術,讓今後想要從事的工程師,應當對乾蝕刻技術具有充分的理解加以面對,並且需求針對初學者的教科書。

本書採用與以往書籍相異的獨特方法,將乾蝕刻技術由基礎到應用,讓初學者能夠理解的加以歸納整理。以往的乾蝕刻書籍,大多動輒偏重於艱深的電漿理論,或是反而從頭到尾羅列乾蝕刻技術的數據。本書的執筆則是盡量不使用數學式,讓初學者也能容易的理解乾蝕刻的機制。此外,由製程直到設備、新技術,考量能系統的理解。更進一步,設置電漿損傷的章節,以便能夠理解全貌,也是特徵之一。

本書不僅讓初學者能容易的理解乾蝕刻技術的原理,也能獲得更切實際的知識。此外,雖然以初學者為對象撰寫,但是對於已經累積某種程度經驗的工程師,在能夠理解乾蝕刻技術的全貌上,期望也能有所助益。本書若能對從事乾蝕刻相關工作的工程師,在工作的執行上給予方針,至感甚幸。

野尻一男

譯者序

譯者就職華邦電子前,曾任職於峰安金屬、林陽實業以及遠東紡織化纖總廠。當有機會聊到自己過去的職涯時,偶而會調侃自己待過金屬、玻璃、紡織、電子等四大產業,剩下養豬業還沒去過(莞爾)。根據個人親身經歷,在電子產業中,光是晶圓廠的半導體前段製程就遠比上述其他三種產業複雜,而且技術的躍進更是日新月異。如果不求進步或轉型,恐怕只有等著關廠、解散一途。

回顧1996年譯者初進半導體業,當時DRAM的量產是以0.45微米技術生產16MB記憶容量的晶片,而如今泛用型DRAM已經使用25奈米的技術量產2GB以上記憶容量的晶片,18年來推進了12個世代。

除了DRAM之外,其它諸如NOR與NAND等大宗的記憶體,以及台灣傲視全球的晶圓代工產業的主力──邏輯IC,也是不遑多讓的朝向微縮、積體化邁進。如同本書所述,其中尤以微影和乾蝕刻為關鍵技術,而乾蝕刻由於牽涉到電漿物理、化學、材料、電磁等複雜的現象,優秀工程師的養成更屬不易。

本書作者具有豐富的業界經驗,深知工程師在專業知識上的需求為何。原書的英文譯本《Dry Etching Technology for Semiconductors》也於2014年10月出版。希望本中文譯本能在半導體乾蝕刻工程師的基礎教育上,略盡棉薄之力。

倪志榮

謹誌於華邦電子中科廠區

謹誌於華邦電子中科廠區

內容連載

第3章 各種材料的蝕刻

在本章,針對實際被使用於半導體製造程序的材料的蝕刻作解說。關於半導體製程的蝕刻大致分為:(1)Si系列的蝕刻;(2)介電層系列的蝕刻;(3)連線材料的蝕刻。在本章,舉例在各範疇中構成基礎技術的閘極蝕刻、孔洞系列的SiO2蝕刻、間隙壁蝕刻以及Al合金層積金屬結構的蝕刻,針對這些作詳細說明。在此並不侷限於只是各論,關於支配蝕刻的參數及其控制方法,也能夠理解的作解說。構成方式是關於這些蝕刻如果能先加以理解,對於其它材料也能有效的應用。例如,在閘極蝕刻,雖然針對Poly-Si閘極、WSi2/Poly-Si閘極、W/WN/Poly-Si閘極的蝕刻敘述,但是如果完全的理解這些,關於STI及W連線等的蝕刻,也能夠以類似的途徑構築製程。而且在閘極蝕刻,不僅是加工形狀,晶圓面內的圖型尺寸的偏差該如何降低,也是強烈的被要求。關於這點,也從支配圖型尺寸的晶圓面內均勻度的參數為何,還有其控制方法為何的觀點,加以解說。

SiO2的蝕刻機制與Si系列不同,而且適合蝕刻的電漿也不同。因此在本章針對蝕刻機制,以及支配蝕刻的關鍵參數,也深入的解說,並且能夠理解氣體系統的構成方法,以及間距狹窄的平行板型蝕刻機被使用的理由等。

在Al連線蝕刻方面,也談論到在製造工程上造成問題的Al腐蝕,並且針對其對策方法作解說。此外,關於連線,取代Al連線的Cu鑲嵌連線技術目前已成為主流,關於這點則在第六章的「新蝕刻技術」中敘述。

3.1 閘極蝕刻

首先一開始針對閘極蝕刻作敘述。閘極蝕刻的工程流程如同已經在第一章的圖1-5所說明。閘極乃決定電晶體特性的重要部分,特別是由於MOS電晶體的臨界電壓(Vth)取決於閘極尺寸,蝕刻完成後的尺寸(CD)的控制非常重要。在65nm之後的節點,邏輯元件的物理上閘極長度變成在45nm以下,接近25nm。在該處,不僅是CD本身的精度,CD的晶圓面內的偏差也強烈的被要求抑制變低。例如,在CD為30nm的閘極,就300mm晶圓面內的CD均勻度(3σ)而言,被要求須在3nm以下。蝕刻形狀理所當然被要求垂直形狀,而且,隨著微縮化的同時,對於愈來愈薄膜化的閘極氧化層,被要求須有高選擇比。就閘極材料而言,在邏輯元件是Poly-Si,而在DRAM則是WSi2/Poly-Si或W/WN/Poly-Si層積結構被使用中。

在本章,針對實際被使用於半導體製造程序的材料的蝕刻作解說。關於半導體製程的蝕刻大致分為:(1)Si系列的蝕刻;(2)介電層系列的蝕刻;(3)連線材料的蝕刻。在本章,舉例在各範疇中構成基礎技術的閘極蝕刻、孔洞系列的SiO2蝕刻、間隙壁蝕刻以及Al合金層積金屬結構的蝕刻,針對這些作詳細說明。在此並不侷限於只是各論,關於支配蝕刻的參數及其控制方法,也能夠理解的作解說。構成方式是關於這些蝕刻如果能先加以理解,對於其它材料也能有效的應用。例如,在閘極蝕刻,雖然針對Poly-Si閘極、WSi2/Poly-Si閘極、W/WN/Poly-Si閘極的蝕刻敘述,但是如果完全的理解這些,關於STI及W連線等的蝕刻,也能夠以類似的途徑構築製程。而且在閘極蝕刻,不僅是加工形狀,晶圓面內的圖型尺寸的偏差該如何降低,也是強烈的被要求。關於這點,也從支配圖型尺寸的晶圓面內均勻度的參數為何,還有其控制方法為何的觀點,加以解說。

SiO2的蝕刻機制與Si系列不同,而且適合蝕刻的電漿也不同。因此在本章針對蝕刻機制,以及支配蝕刻的關鍵參數,也深入的解說,並且能夠理解氣體系統的構成方法,以及間距狹窄的平行板型蝕刻機被使用的理由等。

在Al連線蝕刻方面,也談論到在製造工程上造成問題的Al腐蝕,並且針對其對策方法作解說。此外,關於連線,取代Al連線的Cu鑲嵌連線技術目前已成為主流,關於這點則在第六章的「新蝕刻技術」中敘述。

3.1 閘極蝕刻

首先一開始針對閘極蝕刻作敘述。閘極蝕刻的工程流程如同已經在第一章的圖1-5所說明。閘極乃決定電晶體特性的重要部分,特別是由於MOS電晶體的臨界電壓(Vth)取決於閘極尺寸,蝕刻完成後的尺寸(CD)的控制非常重要。在65nm之後的節點,邏輯元件的物理上閘極長度變成在45nm以下,接近25nm。在該處,不僅是CD本身的精度,CD的晶圓面內的偏差也強烈的被要求抑制變低。例如,在CD為30nm的閘極,就300mm晶圓面內的CD均勻度(3σ)而言,被要求須在3nm以下。蝕刻形狀理所當然被要求垂直形狀,而且,隨著微縮化的同時,對於愈來愈薄膜化的閘極氧化層,被要求須有高選擇比。就閘極材料而言,在邏輯元件是Poly-Si,而在DRAM則是WSi2/Poly-Si或W/WN/Poly-Si層積結構被使用中。

網路書店

類別

折扣

價格

-

新書79折$198

-

新書79折$198

-

新書79折$198

-

新書79折$198

-

新書88折$220

-

新書9折$225

-

新書9折$225